時間:2017-11-23 10:15:10來源:網絡轉載

針對需要切換多個FPGA配置碼流的場合,Xilinx公司提出了一種名為SystemACE的解決方案,它利用CF(CompactFlash)存儲卡來替代配置用PROM,用專門的ACE控制芯片完成CF卡的讀寫,上位機軟件生成專用的ACE文件并下載到CF存儲卡中,上電后通過ACE控制芯片實現不同配置碼流間的切換。

SystemACE的解決方案需要購買CF存儲卡和專用的ACE控制芯片,增加了系統搭建成本和耗費了更多空間,而且該方案只能實現最多8個配置文件的切換,在面對更多個配置文件時,這種方案也無能為力。但若要開發SystemACE的替代方案,則需要選擇更合適的可反復編程存儲器,并且需要選用合適的傳輸協議接口來下載配置碼流。通過串口或并口來下載配置碼流速度太慢,不能滿足應用中快速下載的需要;通過USB接口來下載配置碼流則需要專門的控制芯片,增加了系統設計的成本。

本文選用大容量NORFlash存儲器來存儲配置碼流,并利用JTAG接口完成配置碼流下載的FPGA多配置解決方案。與SystemACE方案相比,該方案不僅能快速完成多個配置碼流的下載,還具有更高的配置速度和更低的實現成本。

1JTAG接口模塊的設計

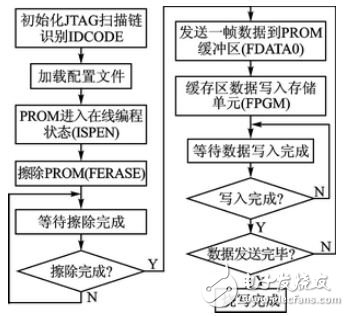

為了將配置碼流寫入Flash存儲器,上位機軟件通過JTAG下載線與JTAG接口模塊連接。JTAG接口模塊接收上位機軟件發送的JTAG信號,從中提取出JTAG指令及對應的數據,并產生針對Flash存儲器的擦除和燒寫信號。由IEEE1149.1-2001標準以及NORFlash存儲器先擦除后寫入的特性,設計上位機軟件的具體執行流程如圖1所示。同時為了完成Flash存儲器的擦除和燒寫,本文在軟件設計中規定了一系列的自定義JTAG指令,如圖1中括號內所示。本文規定一幀數據大小為4096比特。

圖1上位機軟件燒寫Flash存儲器流程

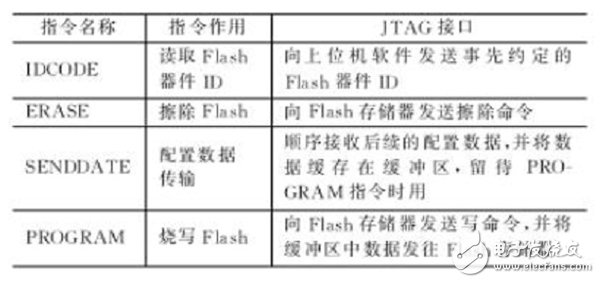

JTAG接口模塊通過外部引腳接收到JTAG信號后,為了完成JTAG指令及數據的提取,JTAG接口模塊中必需包含一個TAP(TestAccessPort)控制器,TAP控制器是一個16狀態的狀態機,在TCK的上升沿通過TMS的變化可以控制狀態的轉移。在特定的狀態即可將JTAG指令及數據分別存入指令寄存器(IRInstrucTIonRegister)和數據寄存器(DRDataRegister)中。JTAG接口模塊在接收到上位機軟件發送的指令后,相應的解釋如表1所列。

表1JTAG指令解釋

2 Flash控制器和FPGA器件配置模塊設計

2.1Flash控制器設計

燒寫Flash存儲器和利用Flash存儲器配置FPGA器件時,都需要對Flash存儲器進行操作,因此需要設計一個控制器模塊來專門產生Flash存儲器的控制指令。Flash控制器要實現的功能是:響應輸入的擦除、寫、讀命令,并根據命令產生相應的時序來實現對Flash的操作。

為了在一片Flash存儲器中存放多個配置文件,可以將Flash按照配置文件的大小分為多個區間。這樣,對于一個具體的配置文件,輸入指令的作用范圍應該在配置文件存放的區間內。因此,擦除某個配置文件時要選用塊擦除方式,而不是整片擦除方式。

為了及時的將一幀配置碼流寫入Flash存儲器中,要求Flash存儲器的編程時間應該小于FPGM指令執行后的等待時間。根據Flash存儲器數據手冊上的參考數據計算后發現,使用普通的編程方式來燒寫一幀配置碼流時間大于等待時間,而使用寫緩沖的編程方式來燒寫一幀配置碼流的時間要小于等待時間,因此必須選用寫緩沖的編程方式來燒寫Flash存儲器。

JTAG接口與Flash控制器間的命令和數據翻譯由反向兼容JTAG控制器中的燒寫控制模塊完成。它會接收JTAG接口發送的擦除或寫命令,經過轉化后產生相應的Flash控制器必需的命令、地址和數據。由于一次寫緩沖編程寫入Flash存儲器的數據小于一幀配置碼流的大小,因此接收到寫命令后,燒寫控制模塊會配合寫命令和對應的操作地址,將緩沖區中一幀配置碼流分多次送往Flash控制器。

2.2FPGA器件配置模塊設計

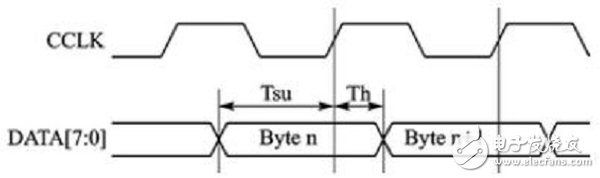

Virtex系列FPGA器件的配置模式共有4種:串行主模式、串行從模式、并行從模式和邊界掃描模式,其中主模式使用內部振蕩器提供時鐘,從模式和邊界掃描模式使用器件外部提供的時鐘。在FPGA器件上電初始化后,配置模塊向FPGA發送配置碼流和配置時鐘來配置FPGA器件。因為配置速度越快FPGA器件工作前的等待時間就越短,所以本方案選擇速度最快的并行從模式[6]。圖2是并行從模式的時序圖,數據(DATA[7:0])必須滿足建立時間(Tsu)和保持時間(Th)的約束。FPGA器件配置模塊配置FPGA器件的步驟如下:

1,FPGA器件配置模塊檢測到INIT引腳信號變高,說明FPGA器件的上電后自動初始化已完成,配置模塊向Flash控制器發送讀命令;

2,配置模塊收到Flash控制器返回的配置碼流后,在每個時鐘上升沿向FPGA器件發送一個8位配置碼流;

3,配置模塊檢測到DONE引腳信號變高,說明FPGA器件已配置完成,配置過程結束。

圖2并行從模式時序圖

4,由于從向Flash控制器發送讀命令到Flash控制器返回配置碼流的時間大于一個周期,且返回數據的位寬大于并行從模式的數據位寬,因此必須先對配置碼流進行位寬轉換。同時,為了保證CCLK的每個始終上升沿都有一個8位配置碼流發送出去,還必須對CCLK進行合適的分頻。

3方案的設計實現

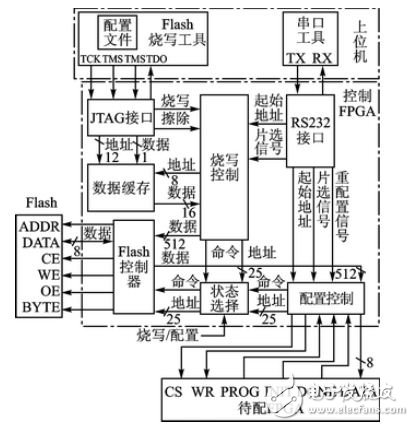

本方案的所有控制邏輯設計用一片XilinxSpartanII系列XC2S200型FPGA器件實現。采用Spansion公司的NORFlash存儲器來存放配置文件,其型號為S29GL512N,容量為512Mb。系統總體框圖如圖3所示。上位機軟件包括Flash燒寫工具和串口工具。燒寫配置文件時,Flash燒寫工具通過JTAG下載線向控制FPGA傳輸JTAG指令及配置碼流,同時串口工具通過串口向控制FPGA發送配置文件地址,完成配置文件存放區間的切換;配置FPGA時,串口工具通過串口向控制FPGA發送配置文件地址及重配置信號,完成配置文件的切換。若實際應用中配置文件過多,還可組成Flash存儲器陣列來增加存儲深度。

圖3系統總體框圖

3.1設計的FPGA實現

控制FPGA實現的邏輯控制功能包括與上位機軟件iMPACT和串口工具通信、燒寫Flash以及配置FPGA器件。基于模塊化的設計思想將具體功能分解成多個模塊,如圖3所示,數據與地址通道上的下標為其通道寬度。各模塊作用如下:

1,RS232接口模塊接收來自串口工具的配置文件地址及重配置信號,配置文件地址譯碼后得到對Flash存儲器進行各種操作時的起始地址,重配置信號則用來觸發FPGA配置文件的切換。

2,JTAG模塊包括JTAG接口模塊、數據緩存模塊及燒寫控制模塊。JTAG接口接收JTAG下載線上的JTAG指令和數據后,若為FERASE或FPGM指令則向燒寫控制模塊發送擦除或燒寫信號,若為FDATA0指令則接收TDI上的串行數據并存入數據緩存模塊中。數據緩存模塊利用片內BRAM來實現,可存放一幀配置碼流。燒寫控制模塊接收到擦除信號后,產生擦除命令和操作地址并發往狀態選擇模塊;接收到燒寫信號后,從數據緩存模塊讀取配置碼流,產生的寫命令、操作地址發往狀態選擇模塊,操作數據則直接發往Flash控制器。

3,FPGA配置模塊接收到來自RS232接口模塊的起始地址和重配置信號后,先向待配FPGA器件發送初始化信號,等待初始化完成后向狀態選擇模塊連續發送讀命令和操作地址,并利用從Flash控制器返回的配置碼流來配置FPGA器件。

4,狀態選擇模塊根據外部的燒寫/配置信號選擇Flash控制器的輸入,從而決定控制FPGA目前處于燒寫Flash存儲器狀態還是配置FPGA器件狀態。若為“0”,則輸入燒寫控制模塊產生的命令和地址,控制FPGA處于燒寫Flash存儲器狀態;若為“1”,則輸入配置控制模塊產生的命令和地址,控制FPGA處于配置FPGA器件狀態。

Flash控制器響應這些輸入的命令、操作地址和數據,產生與命令相對應的Flash存儲器控制時序,并返回Flash存儲器的數據輸出。

3.2性能實際測試

本方案處于編程模式時,系統能夠通過JTAG接口和串口與上位機軟件進行正常的通信,在加載合適的配置文件后,可以完成Flash存儲器的擦除和燒寫操作,實測燒寫速度為160Kb。需要燒寫多個配置文件時,通過串口工具發送配置文件地址,即可對不同的Flash空間進行操作。

處于配置模式時,以Virtex系列中XCV1000型FPGA為配置對象,其配置文件大小約為5.84Mb,實測一次配置時間為60ms,計算得知配置速度約為97Mb/s,遠大于SystemACE解決方案的30Mb/s。如需切換不同的配置文件,從串口工具發送配置文件地址及重配置信號,即可實現多個配置文件的實時切換。

結語

本文分析了各種傳輸協議接口以及SystemACE多配置解決方案的優缺點,根據實際應用需求,提出了一種基于大容量NORFlash并利用JTAG接口完成配置碼流下載的FPGA多配置系統解決方案。本系統采用Flash存儲器替代配置用PROM或CF卡,節省了硬件成本和空間,且理論上可以支持不限數量的配置文件切換,對FPGA的配置速度也達到了SystemACE方案的3倍以上。

標簽:

![]()

上一篇:無線傳感器技術在物聯網領域...

下一篇:淺析步進電機的矩角特性!

中國傳動網版權與免責聲明:凡本網注明[來源:中國傳動網]的所有文字、圖片、音視和視頻文件,版權均為中國傳動網(www.siyutn.com)獨家所有。如需轉載請與0755-82949061聯系。任何媒體、網站或個人轉載使用時須注明來源“中國傳動網”,違反者本網將追究其法律責任。

本網轉載并注明其他來源的稿件,均來自互聯網或業內投稿人士,版權屬于原版權人。轉載請保留稿件來源及作者,禁止擅自篡改,違者自負版權法律責任。

產品新聞

更多>2025-06-16

2025-06-09

2025-06-06

2025-05-19

2025-04-30

2025-04-11