0引言

以太網是當前最基本、最流行的局域網組網技術,為了適應各種新開展的業務如流視頻等,其速率也在不斷提高。千兆以太網是建立在以太網標準基礎之上的技術,具有高效、高速、高性能的特點,目前企業局域網甚至城域網的建設都會把千兆以太網技術作為首選的高速網絡技術。而千兆以太網協議分析技術是隨著計算機技術、現代通信技術、網絡技術的迅速發展而發展起來的,能夠應對信息網絡的突發事件,迅速判斷網絡癱瘓和受攻擊部位,起到應急反應支援的作用。同時,隨著TCP/IP(TransmissionControlProtocol/InternetProtocol)的廣泛應用和深入,TCP/IP計算機網絡的建設、維護和故障診斷面臨著巨大的挑戰,急切需要千兆以太網協議分析技術的應用。

1工作原理

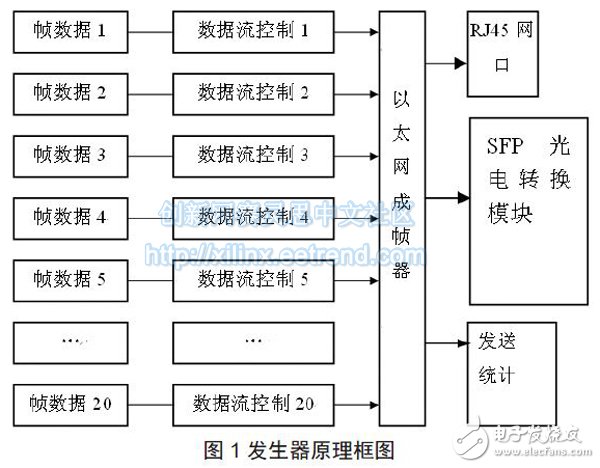

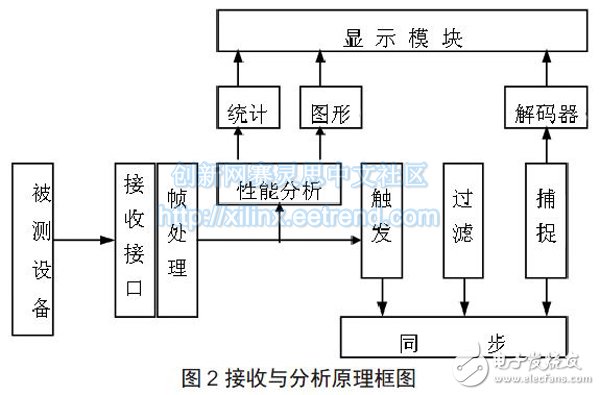

本文介紹的千兆以太網協議分析技術是基于FPGA(Field-ProgrammableGateArray)設計技術,支持10M/100M/1000M電口和光口測試,采用RJ45和SFP光口連接器形式;負責物理層及數據鏈路層的數據幀編輯、生成、捕獲、過濾、觸發、解碼和分析處理工作,IP層以上的協議幀有軟件根據IEEE802.3協議標準進行操作。圖1、圖2所示分別為本方案的發送部分、接收與分析部分的原理框圖。

千兆以太網協議測試FPGA內部設計部分可以分為發送部分、接收分析部分和接口芯片寄存器管理部分。其中,發送部分完成發送、編輯和生成各種以太網數據流等功能,根據測試需要,發送部分可產生任意的MAC地址、IP地址、錯誤的校驗與錯誤插入等非正常數據。其中,MAC地址、IP地址的設置種類很多,可以設置為靜態、遞增、遞減、隨機等;接收分析部分完成以太網數據流統計、捕獲、解碼分析、信號性能統計等功能;根據測試需要,接收部分可選擇捕獲和統計需要的MAC地址、IP地址、錯誤的校驗類型與錯誤插入類型等的數據幀,其中可設置的過濾條件和觸發條件有MAC地址、IP地址、圖形1、圖形2、協議類型和錯誤類型等。接口芯片寄存器管理部分完成對接口芯片BCM5421寄存器的讀寫操作與管理及串/并、并/串轉換功能。

2設計實現

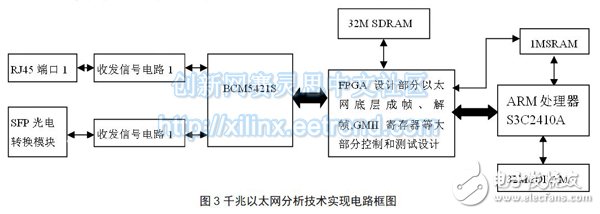

本文介紹的千兆以太網協議分析技術是通過千兆以太網收發器BCM5421和大規模FPGA組合的硬件平臺來實現的。由于千兆以太網支持電口和光口兩種接口方式、以太網協議復雜、千兆速度很高、邏輯控制龐大,在FPGA設計及PCB布板設計實現中,具有很高的難度。具體設計實現的電路框圖如圖3所示。

千兆以太網信號經過收發處理電路送入接口芯片,由接口芯片對信號進行信號有效性、碰撞、編/解碼、點燈等操作,然后以8-bit的串行數據流送入FPGA。在FPGA內需要完成MAC層發送部分各種以太網幀的編輯、生成、數據編輯、錯誤插入、并/串轉換、發送模式的設置等,完成MAC層接收部分各種以太網幀的監測、捕獲、過濾、解碼、查找錯誤和評估性能等,MAC層接口芯片的寄存器管理、讀寫控制等;還有CPU和硬件對SRAM、SDRAM的讀寫、存儲操作等,具體實現過程如下所述。

2.1千兆以太網協議分析接口電路設計

以太網測試模塊采用兩種接口方式:RJ45電口和SFP光電轉換模塊的光口。本技術實現方案采用的是接口收發器芯片BROADCOM公司的BCM5421S,完全支持IEEE802.3、自動協商、碰撞檢測試、編/解碼、串/并變換等功能,符合10BASE-T、100BASE-TX和1000BASET標準。同時,支持RGMII、GMII、MII、TBI、RTBI、SGMII和SerDesMAC接口方式。

2.2千兆以太網協議分析FPGA內部設計

由于千兆以太網協議分析整個工程太大、邏輯控制太復雜、傳輸速率很高,根據設計需要,采用的是Xilinx公司的Virtex4系列的XC4VLX40-11FFG668C,使用VHDL語言進行編程,FPGA主要完成以下功能:

(1)完成10M、100M、1000M三種速率的各種協議層的功能;

(2)幀錯誤和比特誤碼的插入和檢測統計功能;

(3)數據流以太網編/解幀、捕獲、過濾、各種性能指標的計數器及累加功能;

(4)與BCM5421S、微處理器和存儲器(SRAM、SDRAM)之間數據傳送/接收的邏輯控制功能;

(5)與微處理器之間的數據與地址接口控制。

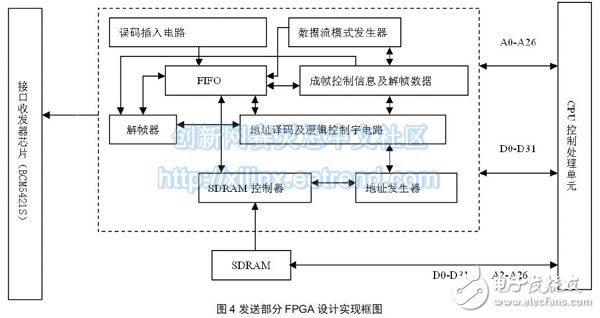

發送部分FPGA設計包括幾個模塊:成幀器模塊、成幀控制信息及幀數據模塊、數據流模式發生器模塊、FIFO模塊、地址譯碼及邏輯控制字電路模塊、誤碼插入電路模塊、地址發生器模塊、SRAM控制器模塊等。

CPU總線分別對SRAM、FPGA內的DPRAM編寫數據流的幀數據及控制信息,通過SRAM控制器對SRAM進行讀寫操作,由于以太網協議的幀長度是以字節為單位的,故需要把SRAM的32位數據轉換為8位,再進行處理。在FPGA內設計一個32位進8位出的FIFO來實現,然后在以太網數據流成幀器模塊中根據數據流控制信息、數據流發送模式、錯誤及BIT誤碼插入等控制信息把以字節為單位的數據流組成滿足各種要求的以太網幀。在成幀的同時,需要對發送的數據幀進行8-bit并行CRC校驗產生一個32-bit的校驗碼,根據幀格式要求加在數據幀的尾部,進而通過8比特輸出到接口芯片,由接口芯片進行編碼輸出。具體實現框圖如圖4的發送部分所示。其中,成幀器中包括前導碼生成模塊、MAC地址生成模塊、協議選擇模塊、IP地址生產模塊、數據域生成模塊等,前導碼長度可從4-255字節任意設置,MAC地址、IP地址可以設置五種生成模式:靜態、遞增、遞減、隨機及本端口(網關),數據域的設置包括固定字、用戶編輯、偽隨機圖形、遞減、遞增和隨機等。

數據流的控制信息都存儲在FPGA中生成的DPRAM中,主要是用來設置每個數據流的控制信息,包括:數據流數據在SRAM中的存放地址、數據流長度、前導碼的長度、發送模式、MAC地址的類型、IP地址的類型、錯誤插入類型、幀間隔及下一個數據流控制信息在DPRAM的地址等。

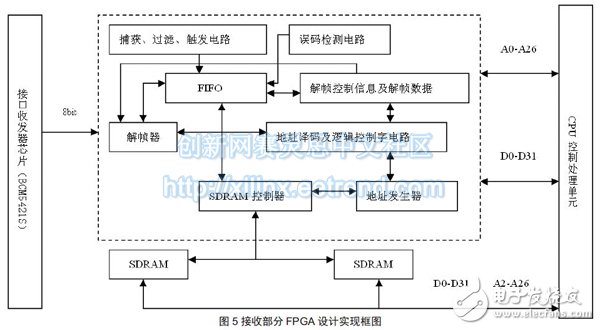

接收部分的FPGA設計主要是用來處理BCM5421S接收的幀數據,對數據流進行解幀、流量控制、性能統計、幀解碼、捕獲、過濾和觸發。其中,過濾和觸發包括源、目的MAC地址,源、目的IP地址,協議類型、幀類型錯誤、圖形1、2等。接收的數據首先根據接口芯片監測的數據速率確定是1000M、100M還是10M信號,將數據流鎖存一個時鐘周期后送入FIFO中,在數據寫入FIFO時仍需記錄每一個數據幀的長度,讀取數據的時候一次讀出整個數據幀。MAC層接收部分FPGA設計包括幾個模塊:解幀器模塊、解幀控制信息模塊、捕獲、過濾、觸發模塊、地址譯碼及邏輯控制字電路模塊、幀錯誤及誤碼監測電路模塊、地址發生器模塊、SDRAM控制器模塊等。具體實現框圖如圖5的接收部分所示。解幀器模塊是成幀器的反過程,根據數據速率的要求選擇不同的時鐘計數器,首先識別前導碼,然后以前導碼結束為依準,運用計數器依次識別MAC目的地址、MAC源目的地址、幀協議類型、數據部分(根據識別后的幀協議類型的不同可以識別不同的幀結構,如IP、TCP、UDP、IGMP、ICMP等幀的幀頭部分)、CRC校驗碼等幀結構中的組成部分,然后分別鎖存在寄存器用于接收數據幀的解碼使用。

在接收數據的接收幀設計的過程中,分別設計了不同的計數器用來對接收幀個數、接收字節數、不同協議幀個數、不同錯誤幀個數等性能指標進行計數,通過軟件每0.5s讀取一次,進行累計或實時統計顯示。

數據幀接收部分的捕獲、過濾、觸發模塊可完成對源、目的MAC地址,源、目的IP地址,協議類型,幀類型錯誤,圖形1、2等指標的捕獲、過濾和觸發功能的測試。幀錯誤及監測電路模塊可以監測發送部分所有能插入的幀錯誤類型,檢測CRC校驗碼的設計程序與發送相同,接收數據經過CRC校驗程序計算以后與發送來的幀CRC校驗碼比較,可以判斷接收的幀數據是否有FCS錯誤。IP、TCP、UDP頭校驗錯誤的監測與FCS錯誤監測類似,不過程序計算校驗和的方法是采用二進制反碼遠算,需要校驗的首部按照16-bit進行相加,如果有進位,就把進位也加上,然后計算和,再取反,就得到校驗和了。地址譯碼及邏輯控制模塊主要是通過軟件對分配好的地址的寄存器進行讀寫即可。

3結束語

本文介紹的千兆以太網協議分析技術采用超大規模FPGA設計技術成功實現千兆以太網數據的發送、接收、協議分析、記錄、統計等功能,設計了采集和存儲快速處理電路,實現了速率為10M/100M/1000M、接口為光口和電口的以太網網絡測試功能,已經成功應用于某測試系統的千兆以太網測試模塊的設計中,并通過了嚴格的測試。

網站客服

網站客服 粵公網安備 44030402000946號

粵公網安備 44030402000946號